0.1UF和10UF电容并联使用的技巧分享

发布日期:2021-11-09

点击次数:2671

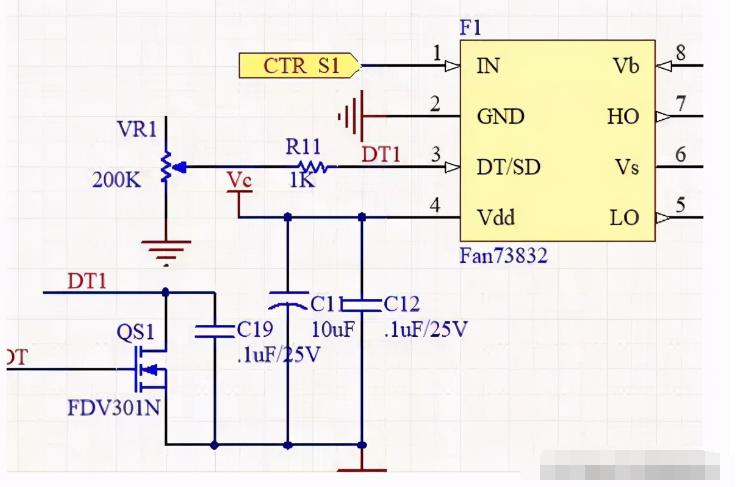

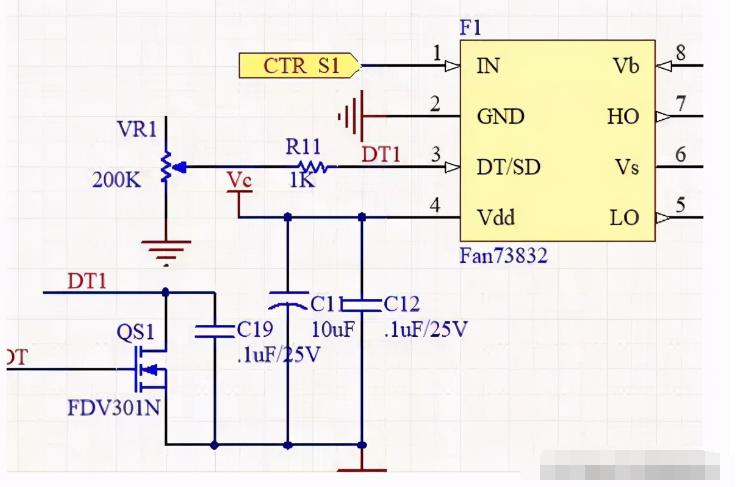

在对某一设计的部分电路进行旁路,双通道(大电容小电容)或是多通道(三个以上的小电容组成,一般在dsp上用得比较多,目的是使频率特性更好。)在电容的接地端,(地线的宽与乍会引起频率的特性),例如在ccd的layout中的bypass,要量电容的接地端的纹波。这就指的是近地端。

在直流馈线中滤出一切交流成分,可将不同的电容并联,滤低频要求电容大,但引线电感不大适合滤高频,滤高频要求电容小,不适合滤低频,如将他们并联可以同时滤除高低频。

有些滤波电路用3个电容并联,分别是电解电容、纸质电容、云母电容,分别滤除电源频率、音频和射频。并联后电容的esr也会小一点。那么电路图中经常有一排排电容,大部分是0.1uf的还有10uf的,这大小和个数多少是怎么算的?

一般说是退耦电容。芯片或者说数字电路开关时候对电源影响大,引起电源波动,就要用电容来退欧。容量一般为芯片开关频率的倒数,如果频率是1MHz的,就选用1/1M,也就是1uF的电容。可以取大点的。最好就是一个芯片一个退偶电容,电源处还要有,用的数量还是挺大的。

在一般的设计中提到电源去耦通常用0.1uF和10uF、2.2uF、47uF,在实际应用中怎么选择?根据不同电源输出还是后续电路呢?

通常情况下,并联两个电容就已经足够了,但对一些电路加上更多的并联电容效果可能会更好。并联不同电容值的电容能确保在一个较宽的频率范围内都得到一个很低的交流阻抗。

在运放的电源抑制(PSR)能力下降的频率范围内,电源旁路尤其重要。电容能够补偿放大器PSR的下降。在很宽的频率范围内,这条低阻通路都能确保噪声不会进入芯片。

在较低的频率下,较大的电容能提供一条到地的低阻通路。一旦那些电容达到自谐振频率,其电容特性消失,转而变成具有电感特性的元件。这就是为什么使用多个电容并联的主要原因,它们能够在很宽的频率范围内保持一个较低的交流阻抗。

电源滤波电路中,将0.1uf和10uf的电容并起来使用,有什么作用?

芯片供电要求电源稳定,而实际电源并不稳定,夹杂高频以及低频干扰。实际电容与理想电容有很大差别,同时具有RLC三性。

10uf电容对于滤除低频干扰有较好作用,但对于高频干扰,电容呈现感性,阻抗很大,无法有效滤除,因此再并一个0.1uf的电容滤除高频分量。如果你的设计要求不高,也没必要完全遵照此规则。

根据经验,电路的总供电原理图,原理图设计时把这些电容画一起,因为它们是同一网络,而到实际PCB设计时,这些电容分别放置到各自作用的IC处。电容容量越大、信号频率越大,电容呈现的交流阻抗越小。

电源(或者信号)或多或少都会叠加一些交流的高频和低频信号,这些交流信号对系统来说是不利的。电容并联放在IC电源脚到地,一般是为了滤除那些对系统不利的交流信号。

10uf的电容和0.1uf一起上是为了使电源(或者是信号)对地的交流阻抗在很宽的频率范围内都很小,这样交流成分能可以被滤除得更干净。

小结:由于实际供电电源,夹杂着高频以及低频干扰杂波,10uf电容对于滤除低频杂波有较好作用,但对于高频杂波,电容呈现感性,阻抗很大,无法有效滤除,因此再并一个0。1uf的电容滤除高频杂波。

免责声明: 本文章转自其它平台,并不代表本站观点及立场。若有侵权或异议,请联系我们删除。谢谢!

矽源特科技ChipSourceTek

中恒科技ChipHomeTek