用于音频数据传输的常见IC间数字接口

发布日期:2022-08-14

点击次数:1876

先了解不同接口的优缺点而后选择元件,这有利于更加合理地选择元件,保证信号链的高效实现。

随着音频集成电路转向更精细的工艺尺度,要在相同一片高密度数字电路硅片上设计出高性能的模拟电路变得更为困难,集成的性价比减小。因此,音频系统架构师正在将音频信号链中的模拟部分进一步推至输出和输入端,而相互间以数码方式连接起来。

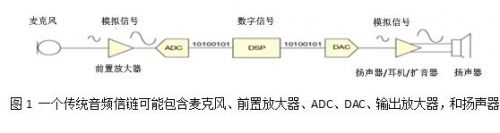

如图1所示,传统的音频信号链中有麦克风、前置放大器、模/数转换器(ADC)、数/模转换器(DAC)、输出放大器,以及扬声器,它们之间使用模拟信号连接。但是,由于模拟电路被推到了信号链的边缘,信号链中各集成电路间将出现更多数字接口。DSP通常是数字连接,换能器、放大器一般而言只有模拟接口,但现在也正在包含数字接口的功能。

目前,集成电路设计人员正在将换能器内的ADC、DAC和调制器集成到信号链的另一端,这样就不必在印刷电路板(PCB)上布放任何模拟音频信号,并且减少了信号链中的器件数量。图2给出了一个完整数字音频信号链的例子。

数字音频数据传输现在有许多标准。很多格式都可以用于在同一块PCB上实现IC间的通信,如I2S(IC间音频)、TDM(时分复用)和PDM(脉冲分时复用)等格式。其它音频格式则主要面向不同印刷电路板之间通过电缆的数据连接,如S/PDIF和以太AVB。

本文的重点是IC之间数字音频格式的区别与优缺点。如选择了数字接口不匹配的音频组件,则会不必要地使系统设计变得更加复杂。了解不同接口的优缺点后再选择部件,有助于提高组件选择效率和保证信号链的最高效实现。

IC之间音频(12S)是用于集成电路之间音频数据传输的最常见数字音频格式。飞利浦半导体(即现在的恩智浦半导体)于1986年推出了12S标准。1996年对该格式进行了修订。该接口首次广泛应用于CD播放器的设计,现在几乎在涉及集成电路间数字音频数据转换的任何应用上都可以看到该接口。多数音频ADC、DAC、DSP,与采样速率转换器,以及一些微控制器都带有I2S接口。

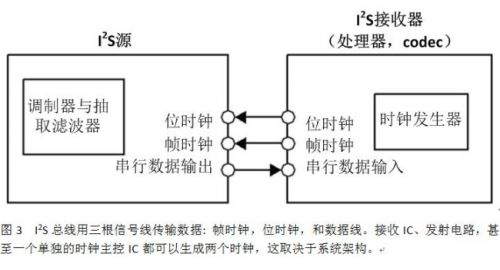

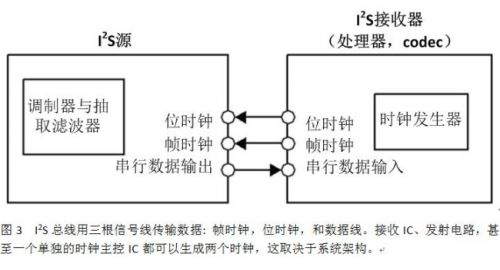

一个I2S总线会使用三根信号线做数据传输:帧时钟,位时钟,以及数据线。接收IC、发送IC,甚至一个单独的时钟主控IC都可以生成两个时钟,这取决于系统架构(图3)。带有I2S端口的集成电路通常可以设置为主模式或从模式。除非设计的信号链中使用了采样率转换器,否则系统通常会有单一的I2S主设备,以避免出现数据同步问题。

对于这些信号,飞利浦标准中将字选择命名为WS,时钟命名为SCK,数据命名为SD,然而电路制造商似乎很少在自己的IC数据表中使用这些名称。字选择另称为LRCLK,表示“左/右时钟”,而SCK则另称为BCLK,指位时钟,或叫SCLK,即串行时钟。

IC串行数据管脚的名称因不同的电路供应商而不同,甚至同一个供应商各产品间的命名也不同。据音频IC数据表的一份快速调查显示,SD信号也可以称为SDATA、SDIN、SDOUT、DACDAT、ADCDAT,或这些名称的其他变体,取决于数据管脚是输入还是输出。

I2S数据流能够以一个典型位时钟速率,携带一个或两个通道的数据,典型的位时钟率在512 kHz(对应8 kHz采样速率)与12.288 MHz(为192 kHz采样速率)之间。数据字的长度通常是16、24,或32位。对于小于32位的数据字长,帧长度一般还是64位,没有用到的位由发送IC驱动至低电平。

有些IC仅支持每个立体声音频帧最大32位或48位时钟的接口I2S,虽然很少见。如果使用这类IC,系统设计人员就必须确保其连接另一端的设备也支持这些位时钟率。

图2 IC设计人员正在换能器中的ADC、DAC和调制器集成到信号链的另一端,从而无需在PCB板上布放模拟音频信号,并减少了信号链上的器件数量。图中是一个完整数字音频信号链的例子。

尽管I2S是最常使用的格式,但也有其它相同三线结构的变体,如左对齐、右对齐和PCM模式。这些格式与I2S的区别在于帧中数据字的位置、时钟的极性,或每个帧中位时钟周期的数量。

TDM格式

有些IC支持使用一个公共时钟的多路I2S数据输入或输出,但这样的方法显然会增加数据传输所需要的管脚数量。当同一个数据线上传输两个以上通道的数据时,就要使用TDM格式。TDM数据流可以承载多达16通道的数据,并有一个类似于I2S的数据/时钟结构。

每个通道的数据都使用数据总线上的一个槽(Slot),其宽度相当于帧的1/N, 其中N是传输通道的数量。出于实用考虑,N通常四舍五入到最近的2次幂(2、4、8、或16),并且任何多余通道都被空闲。一个TDM帧时钟通常实现为一位宽的脉冲,这与I2S的50%占空比时钟相反。超过25 MHz的时钟速率通常不用于TDM数据,原因是 较高的频率会引起印刷电路板设计者要避免的板面布局问题。

TDM常用于多个源馈入一个输入端,或单源驱动多只器件的系统。在前一种情况下,(多源馈入一个输入端),每个TDM源共享一个公共的数据总线。该信源必须配置为在其适用通道期间才驱动总线,而当其它器件在驱动其它总线时,其驱动器要置为三态。

TDM接口还没出现类似飞利浦I2S的其他标准,因此,很多IC都有着自己略微不同的TDM实现方法。这些变化体现在时钟极性、通道配置,以及闲置通道的三态化和驱动上。当然,通常情况下不同IC是可以一起工作的,但系统设计者必须确保一个器件的输出格式要符合另一只器件输入端的预期

PDM数据连接

PDM数据连接在手机和平板电脑等便携音频应用上方面变得越来越普遍。PDM在尺寸受限应用中优势明显,因为它可以将音频信号的布放围绕LCD显示屏等高噪声电路,而不必处理模拟音频信号可能面临的干扰问题。

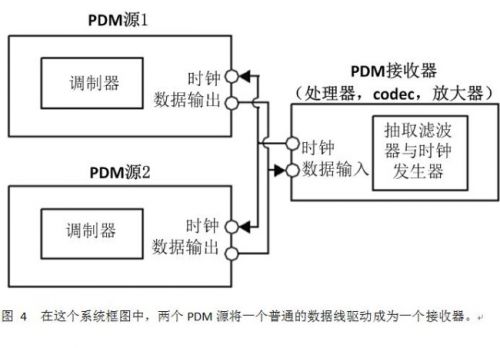

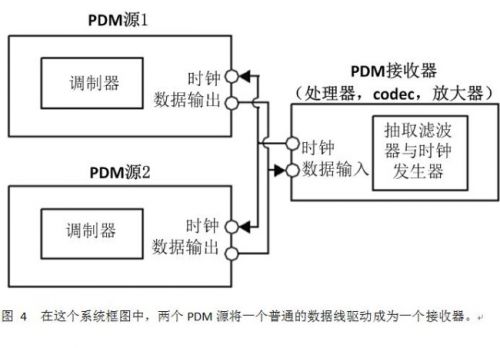

有了PDM,仅两根信号线就可以传输两个音频通道。如图4系统框图所示,两个PDM源将一根公共数据线驱动为一个接收器。系统主控生成一个可被两个从设备使用的时钟,这两个从设备交替使用时钟的边缘,通过一根公共信号线将其数据输出出去。

这些数据调制在一个64×速率上,从而形成一个通常为1到3.2 MHz的时钟。音频信号带宽随着时钟频率的增加而增加,因此,可以在系统中使用较低频率的时钟,从而抵消了为节省功耗而降低的带宽。

基于PDM的架构不同于I2S和TDM之处是,抽取滤波器是不在发送IC中,而是位于接收IC中。源输出是原始的高采样率调制数据,如Sigma-Delta调制器的输出,而不是像I2S中那样的抽取数据。基于PDM的架构减少了源器件的复杂性,通常会利用已经存在于编解码器ADC中的抽取滤波器。

通过这种方法,系统设计者不仅可以利用可能已被使用的音频编解码器, 也可以利用到数字数据连接对干扰不敏感的优点。此外,通过使用面向编码器或处理器制造的更精细硅工艺尺度,而不是用于话筒IC的工艺,就可以实现更高效的抽取滤波器。

编解码器、DPS,和放大器拥有I2S端口很多年了,但直到现在,麦克风等系统输入设备还是模拟或PDM输出。随着数字接口进一步靠近信号链的两端,将需要新的IC来支持新的系统架构。

拥有集成I2S接口的话筒(如Analog Devices公司的ADM441 MEMS话筒)使设计者很容易将该元件做到不容易使用PDM话筒的系统中,或不希望用模拟接口的系统中。只有少部分音频编解码器能接受PDM输入,极少专门针对手机和平板电脑设计的处理器才能原生地接受这种类型数据流。

在有些设计中,一只I2S输出的话筒可以完全无需任何模拟前端电路,因此很多设计可能只有一只ADC和PGA,从而支持话筒对处理器的单个输入。这样一个系统的实例是一种带数据发射器的无线话筒。无线传输SOC可能并没有内置ADC,因此采用一个I2S话筒,就能实现换能器与发射器之间的完全数字化连接。

I2S、TDM与PDM音频接口各有其优点与最适合的应用。随着更多音频IC从模拟接口转向数字接口,系统设计者与架构师们会需要了解哪种接口最适合于自己的特定设计。从话筒到DSP再到放大器,这样一个数字信号链可以完全脱离开PCB,而仅存在于音频域中。

|

免责声明: 本文章转自其它平台,并不代表本站观点及立场。若有侵权或异议,请联系我们删除。谢谢! |