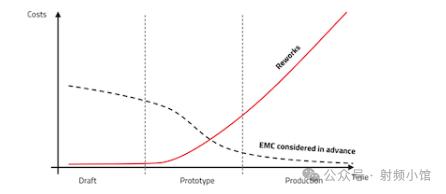

1.越早越好

切勿低估电磁干扰(EMI)问题,因为它们可能耗费大量时间和金钱来解决。你越早关注可能的EMI问题,产品发布就会越快越经济。如果等到最后一刻才解决潜在问题,可能会导致电路板重新设计,或者需要昂贵的解决方案来修复EMI问题。

图1. 提前考虑电磁兼容性(EMC)与否的设计过程成本与时间对比。

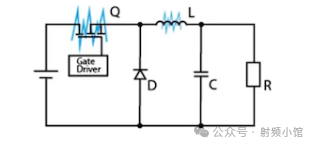

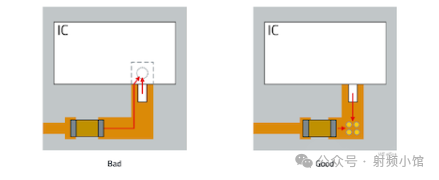

2.将电感器靠近集成电路(IC)

图2. 设计布局的重要性。

输入电容器、开关和二极管形成了一个高电流环路,这是一个H场环形天线。最小的寄生电感和电容会产生高频振铃,这是差模噪声的主要原因。使用低等效串联电阻(ESR)电容器和紧凑的布局可以最小化该环路中传导引起的辐射场。

3.利用电感器的方向优势

MOSFET源极端子、二极管阴极和电感器的连接点是一个热点,该点具有高dv/dt,会形成不良的E场天线。寄生电容允许射频电流流向地面,从而产生共模噪声。同样,这个区域必须最小化。电感器上的点标记表示绕组的起点,即最内层部分,应连接到此节点,以最小化面积、寄生电容,并部分屏蔽它。

图3. Würth Elektronik电感器示例,点标记表示绕组开始的位置。

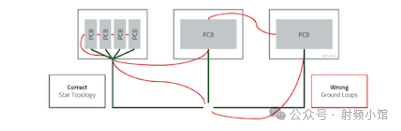

4.地的分布(也称为GND)

注意系统的接地方式。系统的每个部分都应该单独接地。当系统中的任何一点通过多条路径接地时,我们可能会创建一个地环路,这可能会为干扰提供完美的传播路径,从而影响整个设计。当使用长电缆连接不同设备时,这可能会变成辐射发射问题。许多工程师不得不处理电磁兼容性(EMC)问题,原因就在于缺乏合理的接地概念。这种潜在的耦合机制被称为“阻抗耦合”。我们希望在地线和VCC线中的共享阻抗尽可能少。这就是为什么我们通常采用星形拓扑来分布地线。这不仅有助于减少辐射,还有助于提高抗干扰能力!

图4. 正确和错误的接地示例。

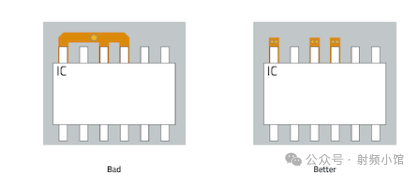

5.IC引脚的地参考

在下面的不良示例中,我们看到两个电路通过IC引脚布线,这可能会导致它们之间产生不必要的耦合。这可以通过使用星形结构的独立电流路径和增加多个过孔来创建短环路进行改进。

图5. 布线电路以减少耦合。

6.降低接地阻抗

每毫米的PCB走线都会增加1纳亨(nH)的寄生电感。这听起来可能不多,但在高频设计中,它会像天线一样起作用,因此变得非常重要。长接地路径会导致寄生电感增加(每毫米1纳亨)。高频时钟IC由于其负载电流而在地上产生干扰电压。为了获得短且低电感的连接,每个引脚都应通过过孔直接连接到地平面。

图6. 在设计中减少接地阻抗。

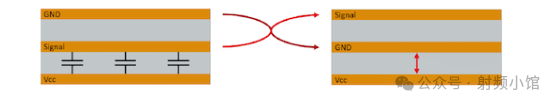

7.GND和VCC层之间的距离

将信号层夹在GND和VCC之间会导致电容耦合。电源上的更高干扰信号水平会耦合到信号位置。纹波电压、负载跳变等会在信号层上产生干扰电压。将GND放置在信号层和VCC之间可以起到屏蔽作用,高频噪声会被直接分流到地。(注意GND需要低阻抗连接。)你可以将VCC和GND之间的距离减少到100微米或更小,以紧密耦合这些层。

图7. 在信号层和VCC之间放置GND。

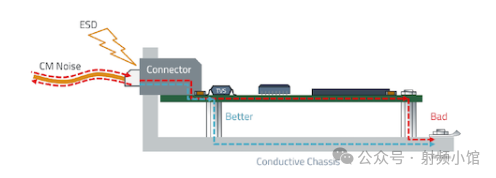

8.将干扰分流到大地

电缆对于共模噪声来说是一个非常好的天线——无论是接收还是发射!

无论是静电放电(ESD)还是共模噪声,都会返回到保护接地/机架接地。将你的PCB连接到机架接地是一个很好的主意,这样可以为这些干扰提供一个明确的回流路径。然而,你不应该只是随意放置这个连接;将其放置在远离其起源的地方会给ESD和共模电流提供影响和损坏你的应用的机会。因此,我们将这些钢质间隔器尽可能靠近I/O端口放置。我们可以放置一个陶瓷安全Y电容,以便在保持直流隔离的同时,实现低阻抗射频耦合到机架。

对于共模发射,这将作为一个短路并保持共模环路小。进入的共模电流和ESD都被分流到远离电子设备的地方。请注意,要确保所有这些连接都是低阻抗的。

图8. 将PCB连接到机架接地的良好和不良示例。

免责声明: 本文章转自其它平台,并不代表本站观点及立场。若有侵权或异议,请联系我们删除。谢谢! |

- Prev:三相无刷电机驱动板,详解三相无刷电机驱动原理及应用

- Next:SOP封装种类和特点