锁相环到底是什么?

Date:December 17, 2023 Views:731

我们大多数人都见过“锁相环”(或其缩写,PLL)这个词。然而,我怀疑我们中很少有人彻底了解 1) PLL 的内部功能以及 2) 该功能如何导致 PLL 的各种使用方式。我在本文中的目标是对基本 PLL 特性提供清晰、直观的解释,我们将继续撰写其他文章来探讨详细信息。

“锁相环”一词出现在多种环境中:微控制器、射频解调器、振荡器模块、串行通信。首先要了解的是,“PLL”并不是指单个组件。PLL 是一个系统— 它由多个经过精心设计并以负反馈配置互连的组件组成。确实,PLL 是作为单个集成电路出售的,因此很自然地将它们视为一个“组件”,但不要因此而分散您的注意力,因为 PLL 类似于(例如)复杂的基于运算放大器的放大器电路,而不是运算放大器本身。

PLL ≥ PD + LPF + VCO

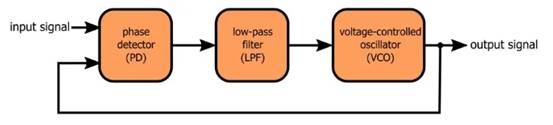

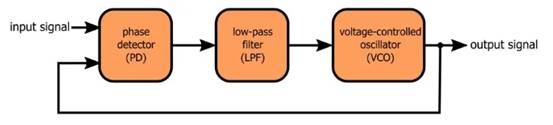

让我们从一张图开始:

锁相环图

这就是 PLL 的基本原理。让我们讨论三个基本组成部分。

相位检测器(不幸的是)并不是真正的相位检测器,但这是标准术语。PLL中的相位检测器实际上是相位差检测器,即,它接受两个周期性输入信号并产生表示两个输入之间的相位差的输出信号。

相位检测器的输出不是与相位差成比例的直接模拟信号。简单的模拟信号就在那里,但它与高频内容相结合,使信号看起来与您可能期望的非常不同。因此需要低通滤波器:它抑制高频分量并将鉴相器的输出转换为可以控制 VCO 的输出。

你猜对了,压控振荡器就是一个由电压控制的振荡器。更具体地,由振荡器产生的周期信号的频率由电压控制。因此,VCO 是一个可变频率振荡器,允许外部电压影响其振荡频率。对于 PLL,控制电压是经过低通滤波的相位检测器信号。

波形

在我们讨论负反馈行为之前,让我们将讨论转移到实际领域。我们将查看数字 PLL 产生的一些波形。您可能会将 PLL 设想为主要是模拟系统,这很好,但尝试数字系统(在我看来)更简单。需要记住的重要一点是,相同的概念适用于模拟和数字实现。如果您了解这些数字波形发生了什么,您就可以大致了解 PLL 信号。

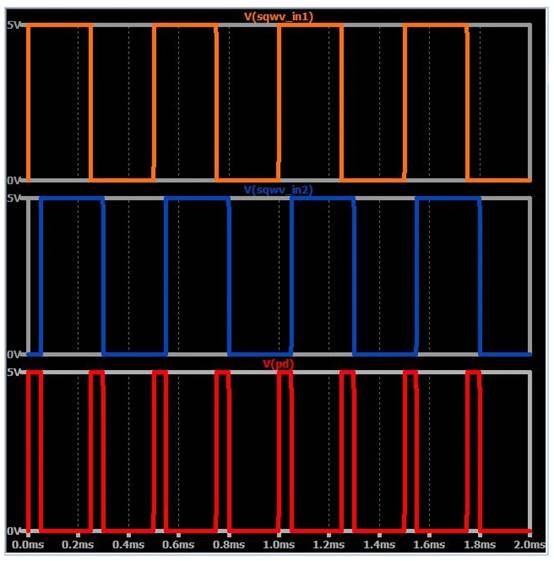

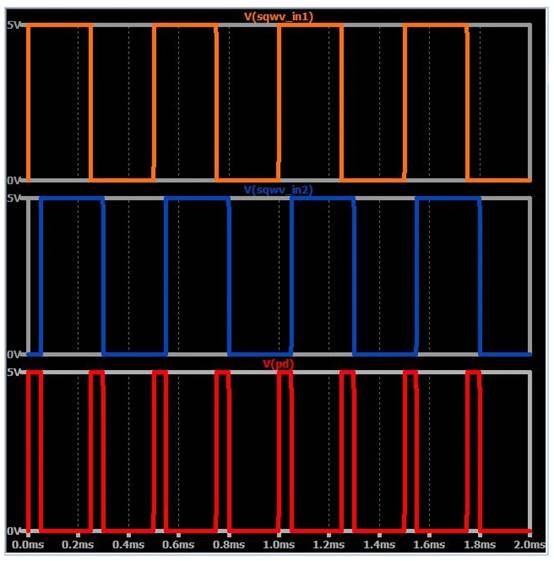

在数字 PLL 中,鉴相器所需的只是一个异或门。如您所知,只有当两个输入不同时,异或门才会产生逻辑高输出。如果将此行为扩展到两个输入均为方波的情况,则 XOR 变为“异相检测器”:

异或门 PLL 图 1

这两个方波具有较小的相位差,因此它们在周期的一小部分内处于不同的逻辑状态。当逻辑状态不同时,XOR 输出为高电平。如果相位差变大,XOR 输出在逻辑高电平上花费更多时间:

异或门 PLL 图 2

这就是异或门作为相位检测器的作用:随着相位差的增加,输出在周期的大部分时间处于逻辑高电平。换句话说,XOR 输出的占空比以及平均值与相位差成正比。

下一步是使用该平均值作为 VCO 的控制信号,这就是低通滤波器的作用:

异或门 PLL 图 3

绿色迹线是带有一点纹波的平均值,是通过将相位检测器信号传递通过简单的 RC 低通滤波器而产生的(如果您使用过“PWM DAC ”,您可能会认识到这种技术,该技术是一种数模转换器,通过对脉宽调制信号进行低通滤波来发挥作用)。该迹线标记为“ctrl”,因为这是我们可以用来控制(即改变其频率)VCO 的信号。

关闭循环

PLL 可以以各种巧妙的方式使用,但基本功能是将输出频率“锁定”到输入频率。(它们还将输出相位锁定到输入相位,正如您从“锁相环”名称中所期望的那样,但它是一种不同类型的锁定。)锁定操作是通过负反馈实现的,即通过路由输出信号返回鉴相器(如上图所示)。

根据我的经验,试图彻底了解 PLL 将输出频率锁定到输入频率的确切过程就像试图抓住一块雾并将其握在手中。它就在你面前,你知道它是真实的,你或多或少知道它是什么,但当你真正尝试观察它并理解它时,它就溜走了。我们将在以后的文章中进一步讨论这个过程。现在,我将向您介绍一些重要的要点,以帮助您思考这个有趣的功能。

仅当两个输入频率相等时(如上例所示),鉴相器才会产生恒定的占空比(因此产生恒定的平均值)。不同的频率会导致占空比周期性变化:

PLL 周期性变化周期 1

PLL 周期性变化周期 2

因此,控制电压将继续上下漂移,直到输出频率等于输入频率。

为了建立锁定,PLL 必须做的不仅仅是使输出频率等于输入频率。它还必须建立输入输出相位关系,以产生适当的控制电压。

PLL 无法直接控制 VCO 信号的相位。调节VCO相位的方法是调节频率,因此频率变化将持续,直到实现频率锁定和相位锁定。

免责声明: 本文章转自其它平台,并不代表本站观点及立场。若有侵权或异议,请联系我们删除。谢谢! |

- Prev:了解您的栅极驱动器

- Next:无刷电机三种控制方式