交错并联的低压大电流DC-DC变换器设计与实现

Date:March 4, 2023 Views:1666

1引言

近年来,随着计算机微处理器的输入电压要求越来越低,低压大电流DC-DC变换器的研究得到了许多研究者的重视,各种拓扑结构层出不穷,同步整流技术、多重多相技术、磁集成技术等也都应用于这个领域。笔者提出了一种交错并联的低压大电流DC-DC变换器,它的一次侧采用对称半桥结构,而二次侧采用倍流整流结构。采用这种结构可以极大地减小滤波电容上的电流纹波,从而极大地减小了滤波电感的大小与整个DC-DC变换器的尺寸。这种变换器运行于48V的输入电压和100kHz的开关频率的环境。

2倍流整流的低压大电流DC-DC变换器的结构分析

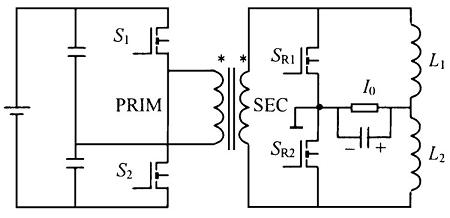

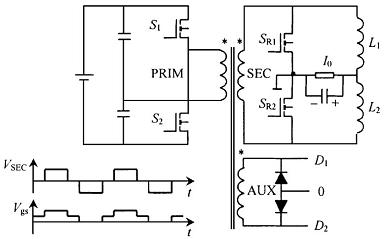

倍流整流低压大电流DC-DC变换器的电路原理图如图1所示,一次侧采用对称半桥结构,二次侧采用倍流整流结构,在S1导通时SR1必须截止,L1充电;在S2导通时SR2必须截止,L2充电,这样滤波电感电流就会在滤波电容上移项叠加。图2给出了开关控制策略。

图1倍流整流的低压大电流DC-DC变换器的电路原理图

图2开关的控制策略

通过以上分析可以看出,倍流整流结构的二次侧2个滤波电感电流在滤波电容上相互叠加,从而使得输出电流纹波变得相当小。

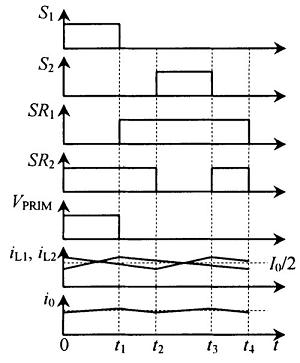

结构中的同步整流器均按外加信号驱动处理,使控制变得很复杂,但在这种半桥-倍流拓扑结构中使用简单的自驱动方式很困难,因为,在这种结构中,如果直接从电路中取合适的点作为同步整流器的驱动信号,在死区时间内当这个驱动信号为零时,同步整流器就会截止。为了在半桥-倍流拓扑结构中使用自驱动方式,就必须使用到辅助绕组。

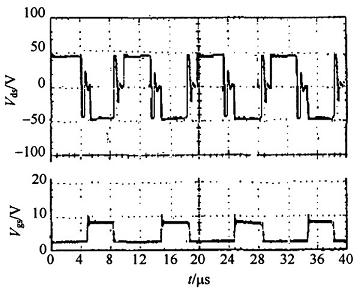

以单个半桥-倍流拓扑结构为例,见图3,VSEC为变压器的二次侧电压,Vgs为由辅助绕组获得的同步整流器的驱动电压,可以看出即使在死区的时间内,同步整流器的驱动电压也不可能为零,保证了自驱动方式在这种拓扑结构中的应用。

图3自驱动同步整流器电路及波形图

另外,由于在大电流的情况下MOSFET导通压降将增大,从而产生较大的导通损耗,为此应采用多个MOSFET并联方法来减小损耗。

3交错并联低压大电流DC-DC变换器

3.1电路原理图

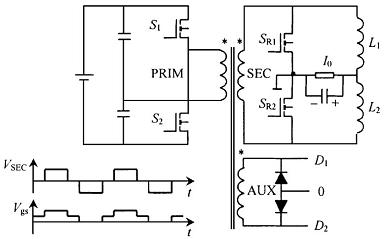

综上所述,倍流整流低压大电流DC-DC变换器具有很好的性能,在此基础上引入交错并联技术,构成一种新的结构,称为并联低压大电流DC-DC变换器,可以进一步减小输出电流纹波。

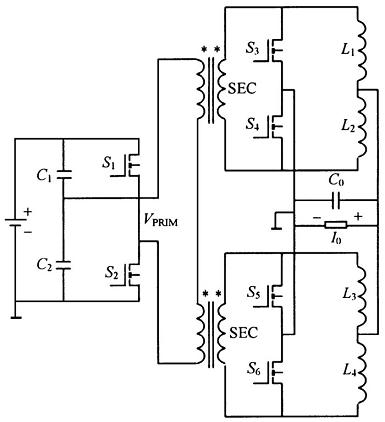

图4为交错并联低压大电流DC-DC变换器的电路原理图(以最简单的2个倍流整流交错并联为例)。

图4交错并联低压大电流DC-DC变换器的电路原理图

3.2变换器的开关控制策略

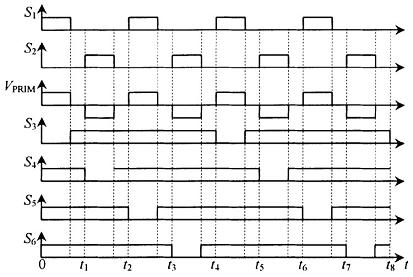

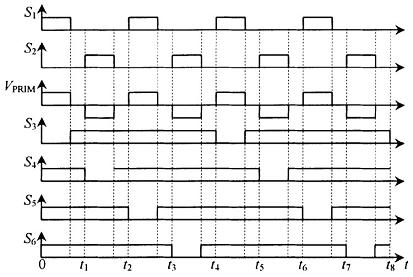

交错并联低压大电流DC-DC变换器的开关控制策略见图5。

图5交错并联低压大电流DC-DC变换器的开关控制策略

3.3交错并联低压大电流DC-DC变换器性能

首先这种拓扑结构最大的优点是变压器原边的结构简化,控制变得很简单。其次,这种方法的实现必须采用同步整流电路,因为交错并联电路的实现要求变压器副边上下电位轮流为正,在一个时间段内有且只有一个为正电位,其余都为零电位。但在这种拓扑结构中,由于2个变压器的原边串联在一起,而副边是并联的,这样如果用肖特基二极管作整流器,那么输入电压将在2个变压器原边上分压,而肖特基二极管又没有选通的功能,这样变压器二次侧的波形将是完全对称的,上下2个整流电路的电流完全重合,达不到电流交错并联的目的。

这样,应用同步整流器来完成这个功能,同时利用MOSFET的双向导电特性,因为同步整流管的漏源电流是分布在坐标横轴两侧的。这种结构的过程详细分析如下:

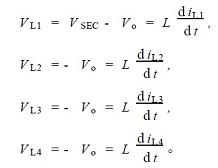

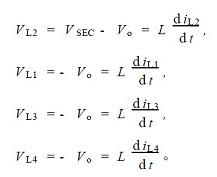

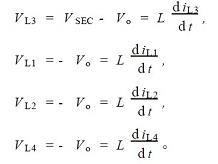

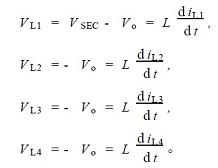

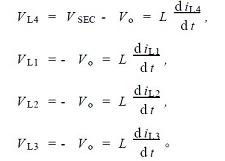

1)S1导通,S2截止;S3截止,S4,S5,S6均导通。由于S4,S5,S6的导通,第一变压器副边绕组下端为零电位,第二变压器副边绕组上、下端均为零电位,电感L1上电流上升,L2,L3,L4上电流下降。

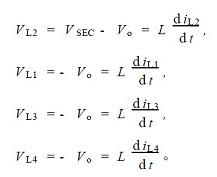

2)S2导通,S1截止;S4截止,S3,S5,S6均导通。由于S3,S5,S6的导通,第一变压器副边绕组上端为零电位,第二变压器副边绕组上、下端均为零电位,电感L2上电流上升,L1,L3,L4上电流下降。

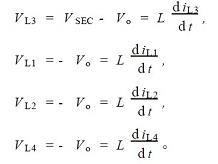

3)S1导通,S2截止;S5截止,S3,S4,S6均导通。由于S3,S4,S6的导通,第二变压器副边绕组下端为零电位,第一变压器副边绕组上、下端均为零电位,电感L3上电流上升,L1,L2,L4上电流下降。

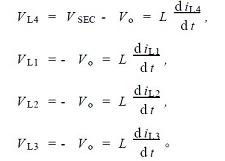

4)S2导通,S1截止;S6截止,S3,S4,S5均导通。由于S3,S4,S5的导通,第二变压器副边绕组上端为零电位,第一变压器副边绕组上、下端均为零电位,电感L4上电流上升,L1,L2,L3上电流下降。

以上各式均忽略整流器的电压降,且VSEC为变压器二次侧的电压值。

根据以上分析可知,应用同步整流器,通过变压器原边串联而副边并联的方法,可以实现这种交错并联半桥-倍流拓扑结构。它的优点主要有以下几个方面:

1)有效地简化了拓扑结构和控制策略。

2)在频率保持不变的情况下,如果纹波的峰-峰值一定,则这种结构可以有效减小滤波电感的值,从而加快整个变换器的动态响应时间。

3)交错并联的半桥-倍流拓扑结构与非交错并联的半桥-倍流拓扑结构相比,一次侧和二次侧的导通损耗相差不多,但由于采用交错并联技术,二次侧的开关频率是原来的一半,相应的开关损耗也是原来的一半。由于变换器的开关损耗在整个损耗统计中占很大的比例,因此,交错并联技术可以极大地提高变换器的效率。

4仿真分析

应用Pspice软件对电路进行仿真。电路的参数如下:开关频率为100kHz,占空比为40%,输入电压为48V,滤波电感为2μH,滤波电容为820μF,输出电流为60A,输出电压为1125V。

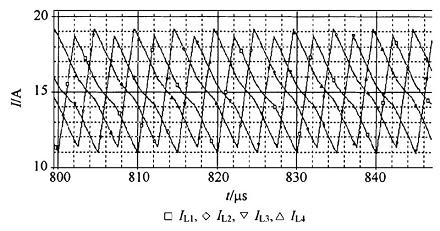

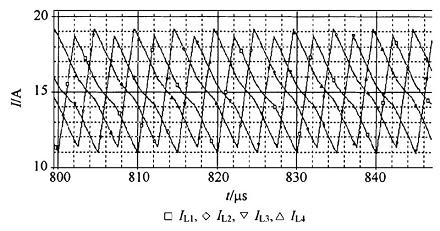

图6所示为滤波电感的电流波形,从图6可以看出,4个滤波电感的电流轮流充电,如果一个滤波电感在充电,其余3个电感必须在放电,在死区时间内,4个滤波电感都在放电。

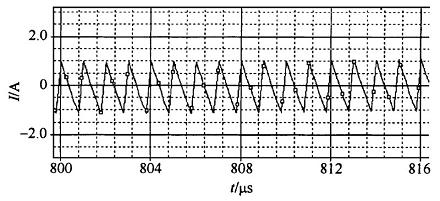

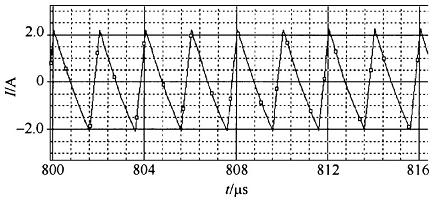

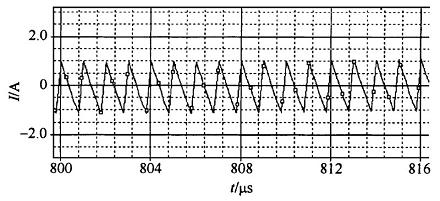

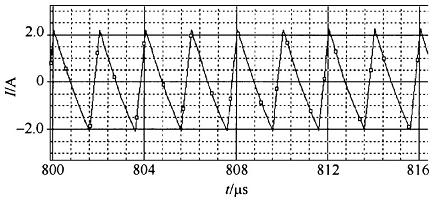

图7和图8所示分别为交错并联变换器与单个倍流整流变换器结构的输出电流纹波波形,从图7中可以看出,4个滤波电感的电流在滤波电容上叠加,可以把电流的纹波减小很多。

图6滤波电感电流波形

图7交错并联变换器结构的输出电流纹波波形

图8单个倍流整流变换器结构的输出电流纹波波形

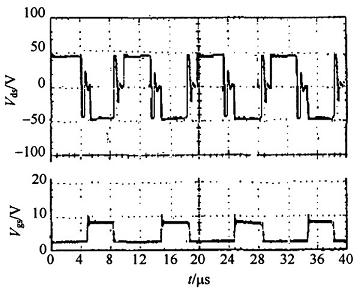

5实验结果

通过理论研究及仿真分析,可以看出,交错并联的低压大电流DC-DC变换器具有良好的性能,在输出为1125V/60A的情况下,输出电流纹波可以降到很小。为了进一步说明这种拓扑结构的可行性,用实验结果验证。实验电路见图4,实验参数和仿真相同,最后得到如图9所示的实验波形。图9中,Vgs为一次侧一个MOSFET的门极驱动电压波形,Vds则为相应的MOSFET的栅源电压波形,从图9可以看出,实验结果所得波形同图5的理论分析结果十分吻合,所提出的方法是可行的。其中,变压器选用R2KB软磁铁氧体材料制作的GU22磁心,原副边的匝数分别为8匝和1匝;电感选用宽恒导磁材料IJ50h制作的环形铁心T5-10-215,匝数为8匝。

图9实验波形

6结语

通过仿真及实验分析,得出以下结论:对于低压大电流DC-DC变换器,可以通过交错并联的方法,进一步减小输出电流纹波,效果十分明显;或者在同样输出电流纹波情况下,可以极大地减小滤波电感值,从而减小整个变换器的尺寸,提高变换器的瞬态响应特性。所讨论的2个倍流整流结构交错并联案例同样适应于多个倍流整流结构交错并联的情况。

- Prev:高电压输入的降压DC-DC变换器

- Next:在3D打印机中推动步进电机的极限控制